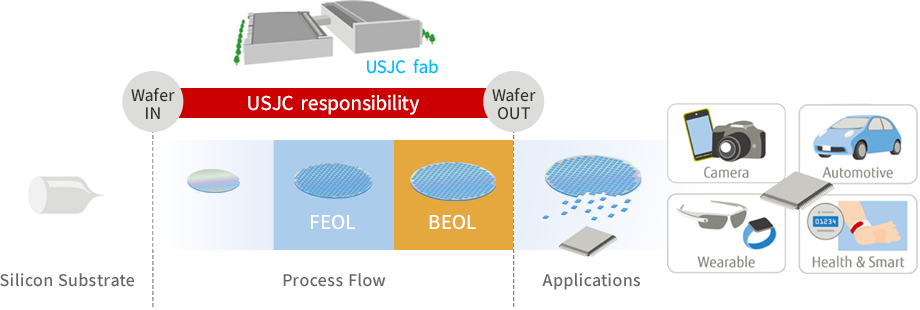

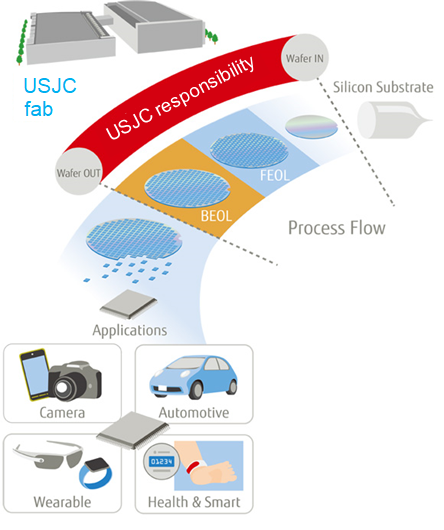

半導体ウェハーができるまで

半導体ICの製造には、数百もの微細加工工程を経てICとなります。

ここではICが出来るまでの(工程)Process Flowの概要を説明します。

Process Flow(プロセスフロー)

Process Flowでは、半導体ICができるまでの流れを、ファウンドリ会社として当社が受託する工程の概要を説明します。

FEOL(Front End of Line:基板工程、半導体製造前工程の前半)

シリコン基板上にトランジスタなどの素子を形成します。

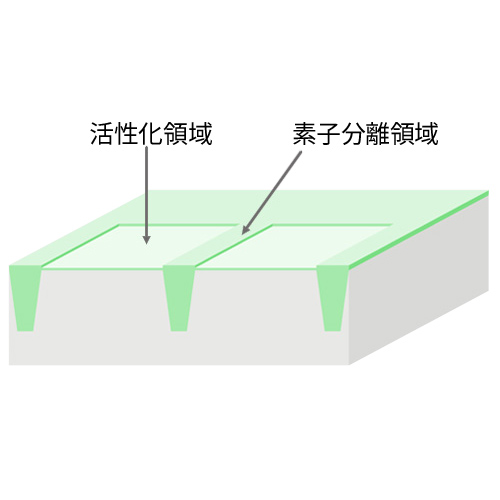

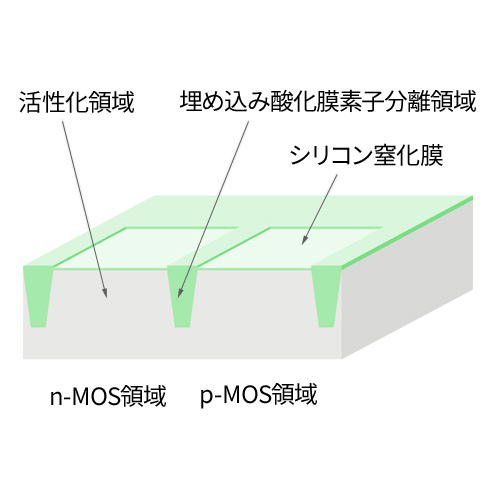

- 1素子分離

-

素子分離

-

トランジスタはシリコンウェハー表面付近に作ります。

個々のトランジスタが独立して動作するよう、隣り合う他のトランジスタとの干渉を防止する必要があります。そのため、トランジスタを形成する領域を分離します。

その素子分離はいくつかの方式があります。

ここで紹介しているのはSTI(Shallow Trench Isolation)という技術です。 -

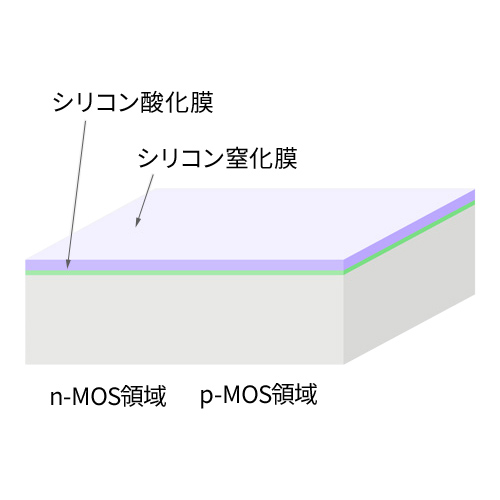

1. 酸化+窒化膜成長

シリコンウェハーを酸化しシリコン酸化膜を形成し、続いてCVD法でシリコン窒化膜を形成します。

-

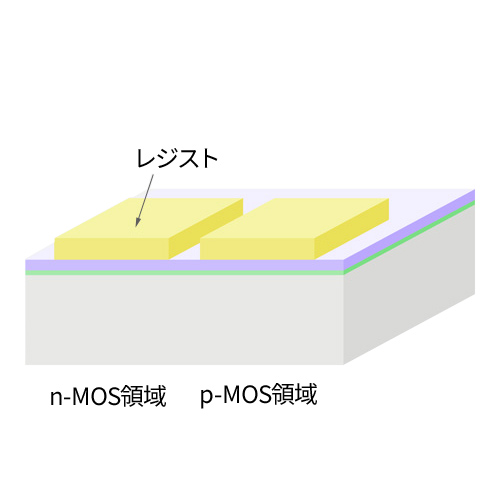

2. レジストパターン形成

レジストパターンを形成します。

-

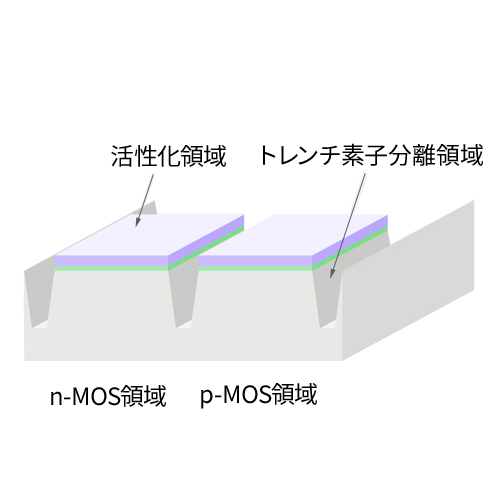

3. 浅溝形成

レジストパターンをマスクにシリコン窒化膜、シリコン酸化膜、シリコンウェハーをエッチングし、浅い溝(trench、トレンチ)を掘ります。

溝を掘った後、レジストパターンは除去します。 -

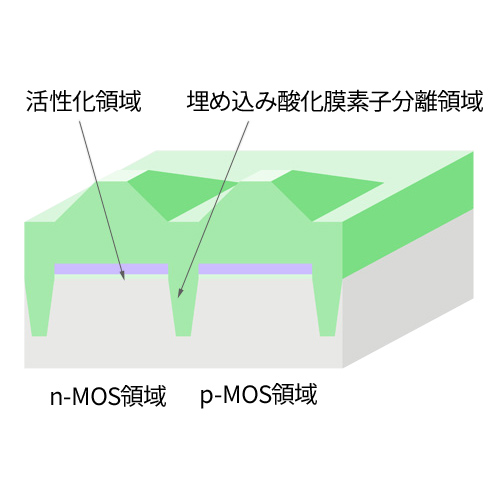

4. 埋め込み酸化膜成長

CVD法で厚いシリコン酸化膜を形成し溝を埋めます。

-

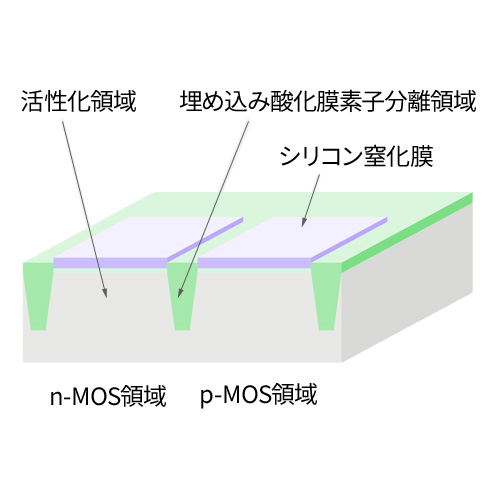

5. 埋め込み酸化膜研磨

表面を研磨し余分なシリコン酸化膜を除去し、溝の中だけにシリコン酸化膜を残します。

-

6. 窒化膜除去

薬品処理でシリコン窒化膜を除去します。

-

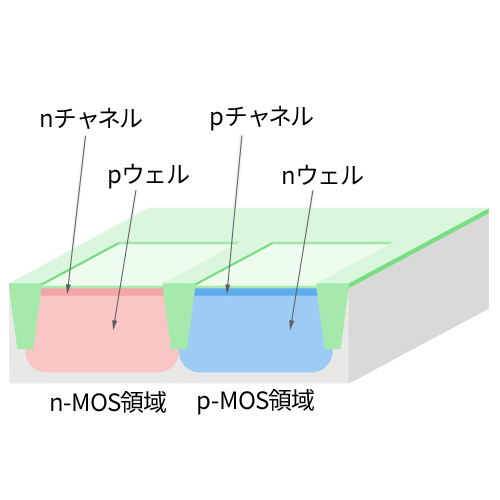

- 2ウェル+チャネル形成

-

ウェル+チャネル形成

-

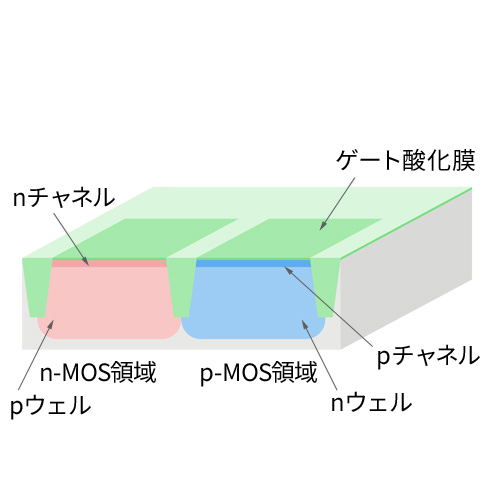

ひとつのチップの中にn型MOSトランジスタ、p型MOSトランジスタを作り分けます。

トランジスタを作る領域にそれぞれのトランジスタに応じた不純物を適切な濃度で注入します。(n-MOS:pウェル、nチャネル、p-MOS:nウェル、 pチャネル)また、異なる電圧/特性のトランジスタを作るときは異なる不純物/濃度の注入を追加することで作り分けます。 -

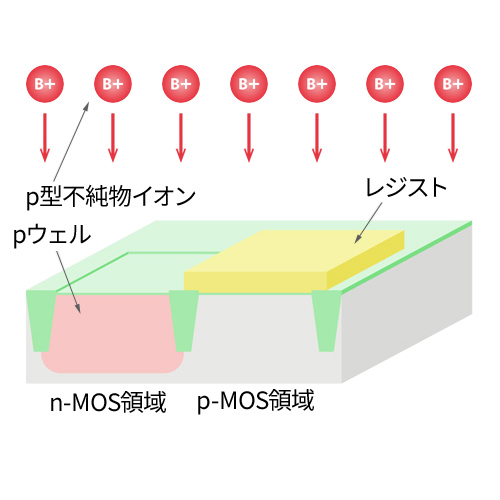

1. pウェル

p-MOS領域を覆うレジストパターンを形成し、n-MOS領域にp型不純物(B ボロンなど)を注入します。

注入後、レジストパターンは除去します。 -

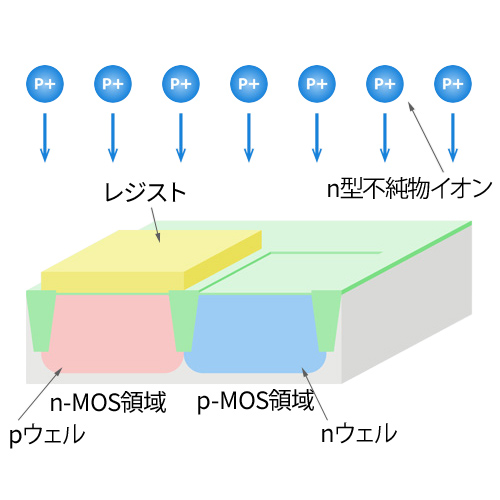

2. nウェル

n-MOS領域を覆うレジストパターンを形成し、p-MOS領域にn型不純物(P リンなど)を注入します。

注入後、レジストパターンは除去します。 -

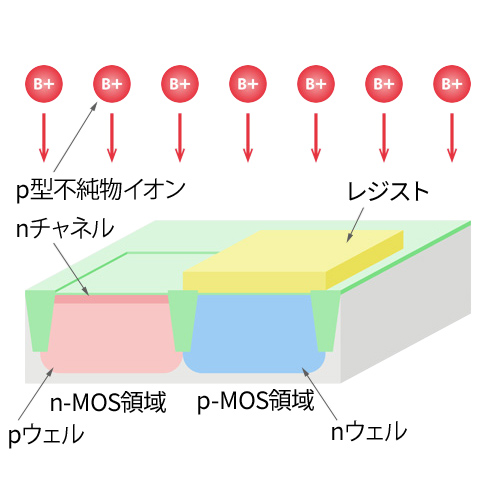

3. nチャネル

p-MOS領域を覆うレジストパターンを形成し、n-MOS領域にp型不純物(B ボロンなど)を注入します。

注入後、レジストパターンは除去します。 -

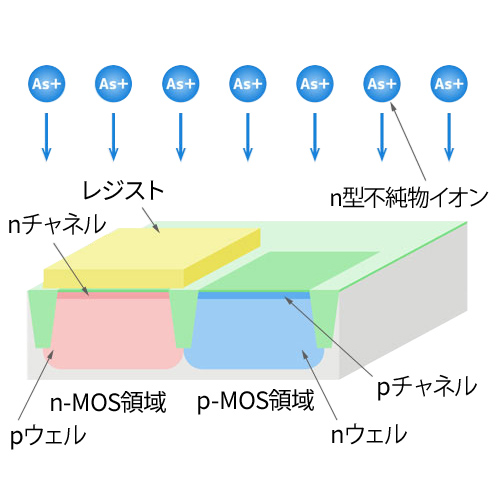

4. pチャネル

n-MOS領域を覆うレジストパターンを形成し、p-MOS領域にn型不純物(As ヒ素など)を注入します。

注入後、レジストパターンは除去します。

-

- 3ゲート酸化+ゲート形成

-

ゲート酸化+ゲート形成

-

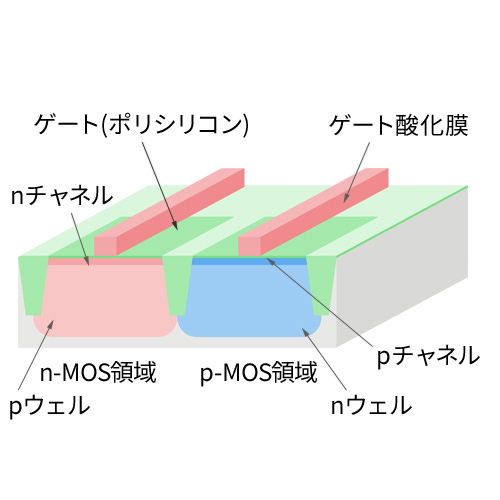

トランジスタの性能を左右するもっとも重要な工程です。

ゲート酸化はトランジスタの性能、信頼性に大きく影響するため、均一な分布の薄く緻密な膜である必要があります。

ゲート形成の寸法もトランジスタの性能に大きく影響するため、レジストパターン形成、エッチングともに厳密な寸法管理が必要です。

なお、ゲート電極はポリシリコン(多結晶シリコン)をCVD法で形成します。 -

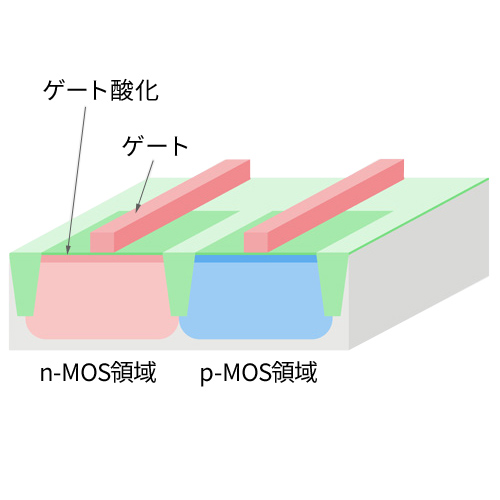

1. ゲート酸化

薬品処理で清浄な状態になったシリコン表面を酸化し、ゲート酸化膜を形成します。

この酸化膜の膜厚/膜質はトランジスタの性能、信頼性に大きく影響するため、均一な分布の薄く緻密な膜である必要があります。 -

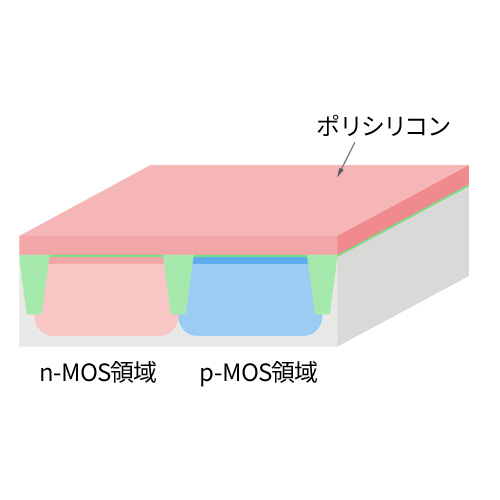

2. ポリシリコン成長

ゲート電極となるポリシリコン(多結晶シリコン)をCVD法で形成します。

-

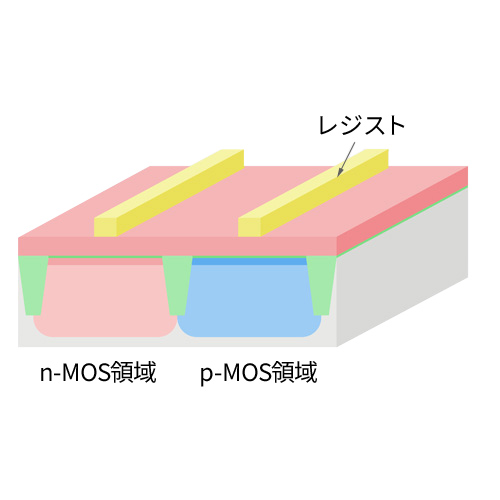

3. ゲートレジストパターン形成

ゲートレジストパターンを形成します。

-

4. ゲートエッチング

ゲートレジストパターンをマスクにポリシリコン、ゲート酸化膜をエッチングしゲートを形成します。

エッチング後、レジストパターンは除去します。

ゲートの寸法はトランジスタの性能に大きく影響するため、ゲートレジストパターン形成、ゲートエッチングともに厳密な寸法管理が必要です。

-

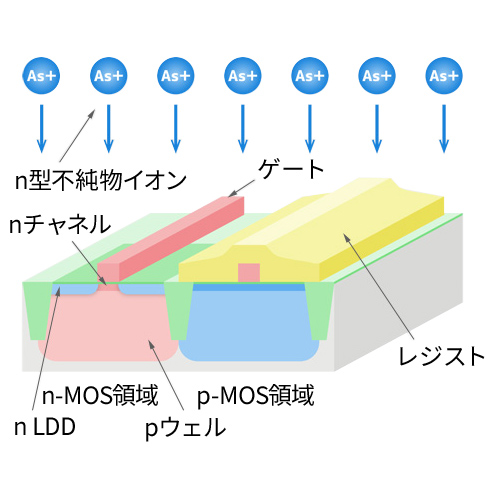

- 4LDD形成

-

LDD形成

-

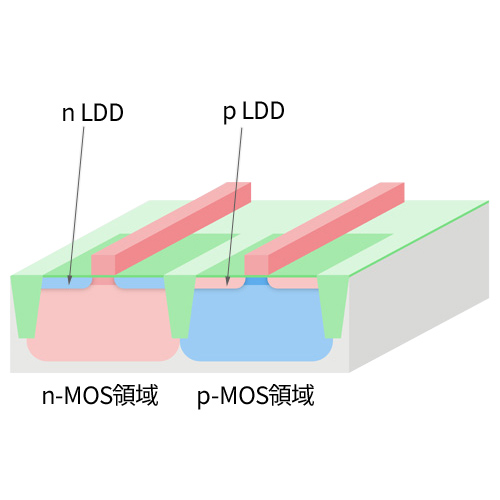

トランジスタの微細化にともなう弊害(動作速度が遅くなるなど)を回避するため、LDD(Lightly Doped Drain、低濃度不純物ドレイン)を形成します。

LDDはエクステンションとも言います。

n-LDD:n-MOS領域にn型不純物(リン、ヒ素など)を注入します。

p-LDD:p-MOS領域にp型不純物(ボロンなど)を注入します。 -

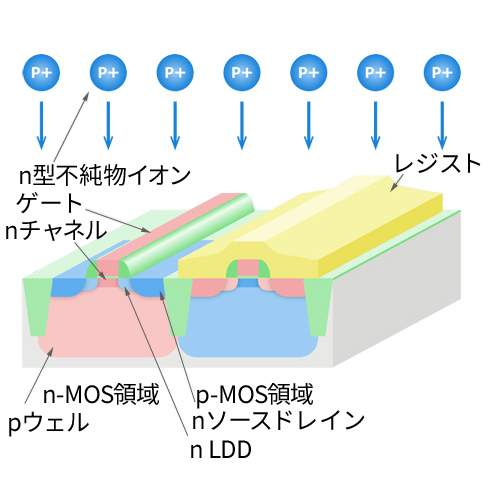

1. n-LDD

p-MOS領域を覆うレジストパターンを形成し、n-MOS領域にn型不純物(P リン、As ヒ素など)を注入します。

注入後、レジストパターンは除去します。 -

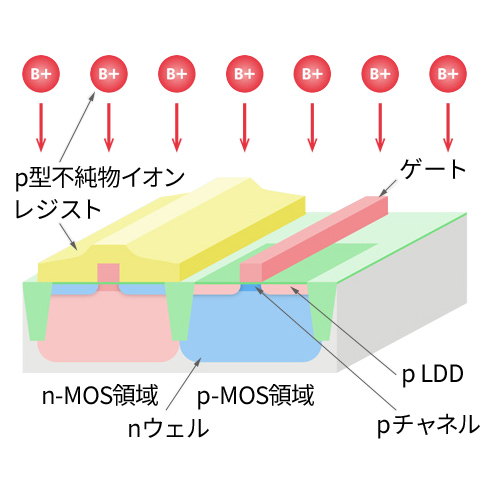

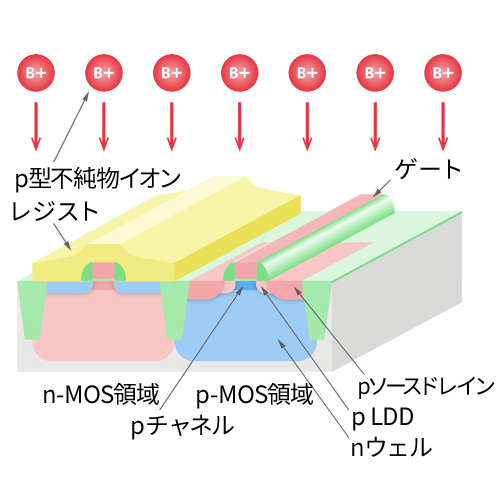

2. p-LDD

n-MOS領域を覆うレジストパターンを形成し、p-MOS領域にp型不純物(B ボロンなど)を注入します。

注入後、レジストパターンは除去します。

-

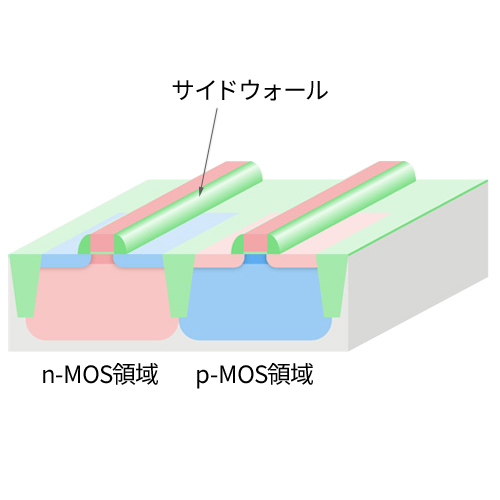

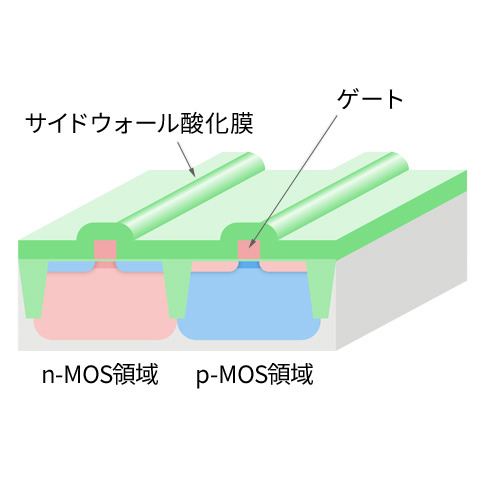

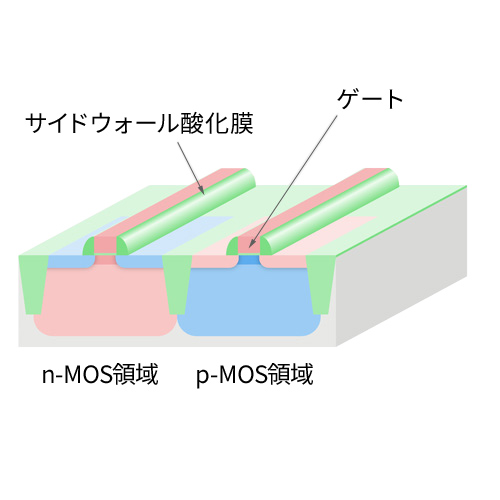

- 5サイドウォール

-

サイドウォール

-

前記のLDD形成および、ゲート、ソース、ドレインのサリサイド形成(後述)を成立させるため、ゲートの横方向(両サイド)の壁のみに酸化膜を形成します。

サイドウォール酸化膜成長:ウェハー全面に酸化膜を形成します。

サイドウォールエッチング:酸化膜に異方性(縦方向)のエッチングを施しゲート側壁のみに酸化膜を残します。 -

1. サイドウォール酸化膜成長

シリコンウェハー全面に、CVD法でシリコン酸化膜を形成します。

-

2. サイドウォールエッチング

全面に形成した酸化膜に異方性のエッチングを施すと、ゲート側壁のみに酸化膜を残すことができます。

このようなレジストパターンを用いないエッチングは、エッチバックと言います。

-

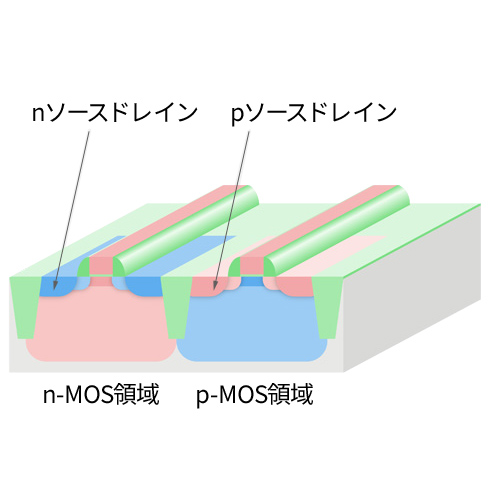

- 6ソースドレイン

-

ソースドレイン

-

n-MOS領域、p-MOS領域それぞれにソースとドレインを形成します。通常のトランジスタの場合、左右対称であるため形状は同じです。電源の接続方向によってどちらがソースでドレインなのかが規定されます。

p-ソースドレイン:p-MOS領域にp型不純物(ボロンなど)を注入します。

n-ソースドレイン:n-MOS領域にn型不純物(リン、ヒ素など)を注入します。 -

1. p-ソースドレイン

n-MOS領域を覆うレジストパターンを形成し、p-MOS領域にp型不純物(B ボロンなど)を注入します。

注入後、レジストパターンは除去します。 -

2. n-ソースドレイン

p-MOS領域を覆うレジストパターンを形成し、n-MOS領域にn型不純物(P リン、As ヒ素など)を注入します。

注入後、レジストパターンは除去します。

-

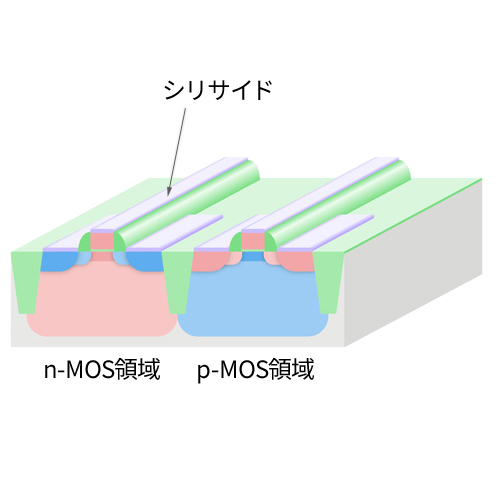

- 7シリサイド

-

シリサイド

-

MOSトランジスタの三つの電極であるゲート(ポリシリコン)、ソース、ドレイン(シリコンウェハー)をシリサイド(金属との化合物)化することでこの後の金属配線との抵抗を下げます。また、それぞれの電極自体の抵抗を下げる効果もあります。

サリサイド形成:薬品処理で選択的にコバルトだけを除去(自己整合でシリサイド形成)します。 -

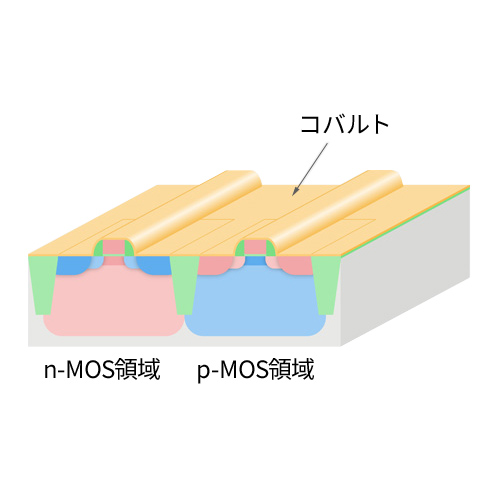

1. コバルト成膜(スパッタ)

シリコンウェハー表面にをPVD法(スパッタ)でコバルト膜を形成します。

シリサイドに用いる金属はコバルト以外にもニッケル、チタンなどがあります。 -

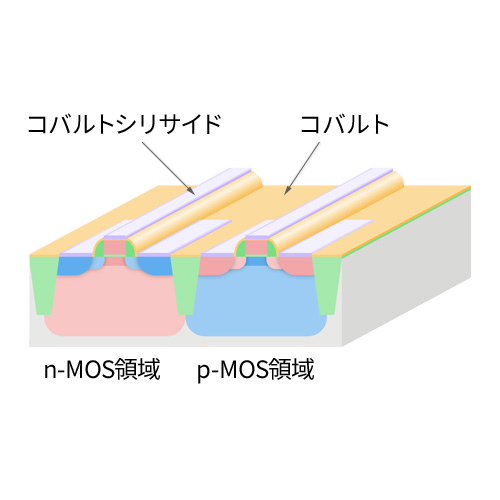

2. コバルトシリサイド化

表面にコバルト膜が乗ったシリコンウェハーを加熱すると、シリコンとコバルトの接している部分が、コバルトシリサイドに変化します。

酸化膜上のコバルトはコバルトのままです。 -

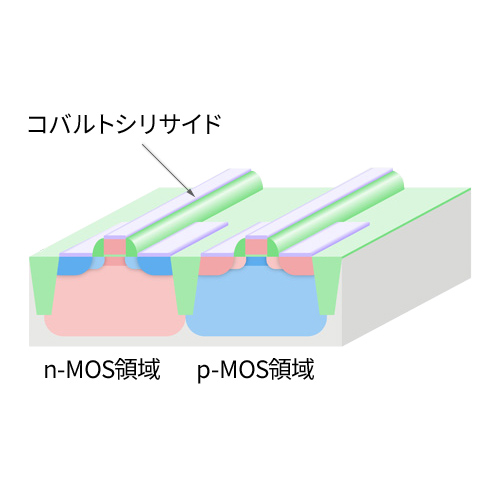

3. コバルト除去

薬液処理で、選択的に酸化膜上のコバルトだけを除去します。

ゲート、ソース、ドレイン上のシリサイドが残ります。このように自己整合でシリサイドを形成することを、サリサイド(Self Aligned Silicide)と言います。

-

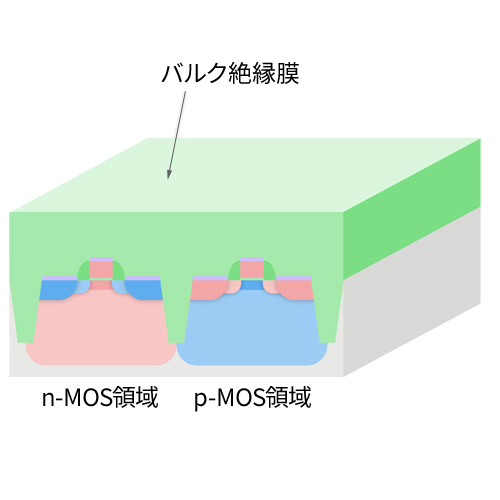

- 8絶縁膜

-

絶縁膜

-

ここからはトランジスタなどの素子を接続する配線工程になります。

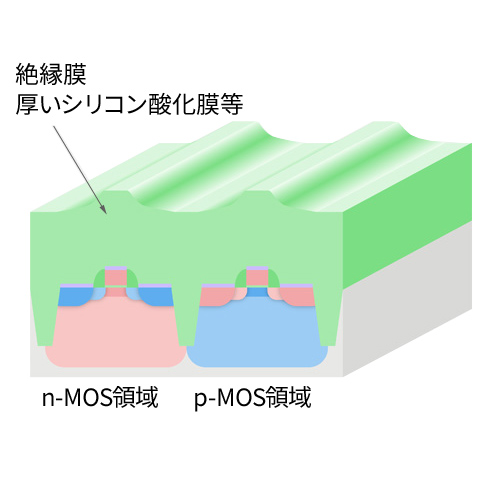

絶縁膜形成:CVD法で厚いシリコン酸化膜などを形成します。

絶縁膜研磨:ウェハー表面の凸凹を平坦化するため酸化膜を研磨します。 -

1. 絶縁膜形成

シリコンウェハー表面に、CVD法で厚いシリコン酸化膜などを形成します。

-

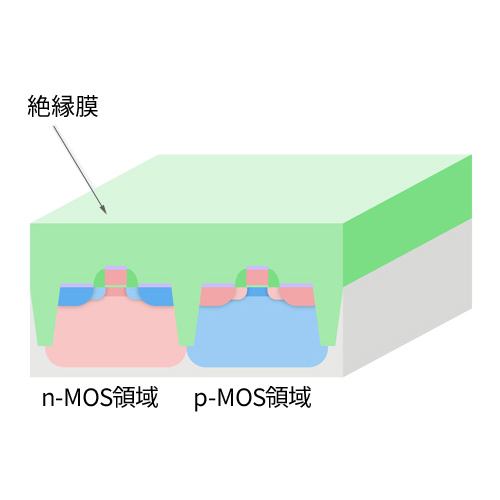

2. 絶縁膜研磨

絶縁膜を形成しただけではウェハー表面は凸凹で、この後の加工に支障をきたします。平坦化するため、表面の酸化膜を研磨します。

-

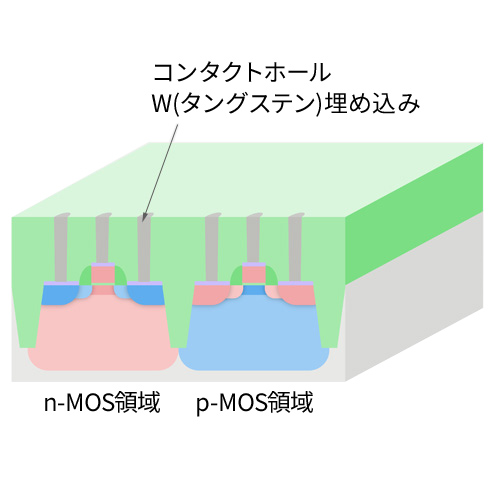

- 9コンタクトホール

-

コンタクトホール

-

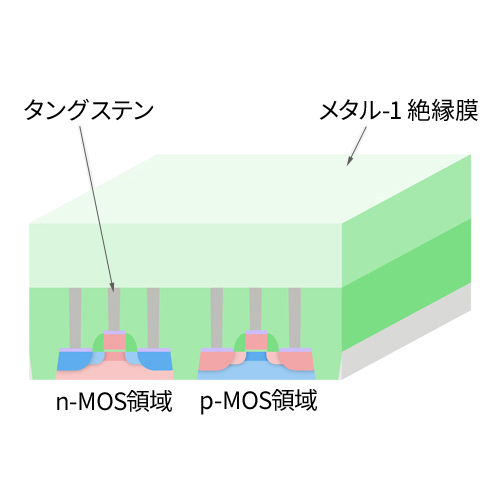

トランジスタのゲート、ソース、ドレインなどの電極を絶縁膜上に引き上げるため、絶縁膜に穴(コンタクトホール)を開け、W(タングステン)を埋め込みます。

タングステンプラグ埋め込み:穴にタングステンを埋め込みます。

タングステンプラグ研磨:表面を研磨し余分なタングステン膜を除去し、穴の中だけにタングステンを残します。 -

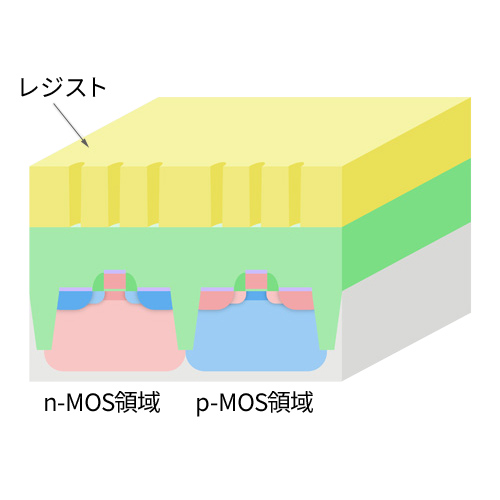

1. コンタクトホールレジストパターン形成

コンタクトホールのレジストパターンを形成します。

-

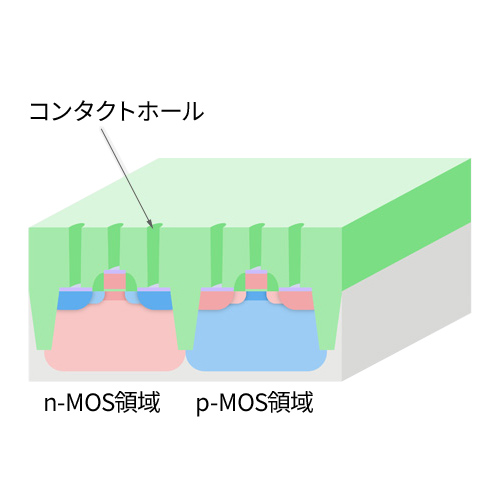

2. コンタクトホールエッチング

コンタクトホールレジストパターンをマスクにエッチング処理をおこない、絶縁膜にコンタクトホールを形成します。エッチング後、レジストパターンは除去します。

非常に小さくて深い(アスペクト比が高い)穴であるため、穴の径、深さの管理には細心の注意を払う必要があります。 -

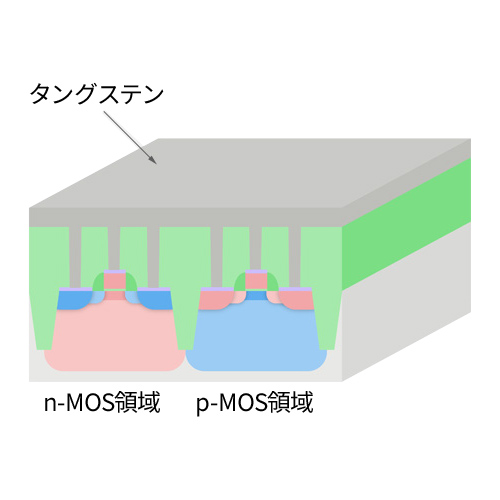

3. プラグタングステン埋め込み

シリコンウェハー表面にCVD法でタングステン膜を形成し、コンタクトホールに埋め込みます。

-

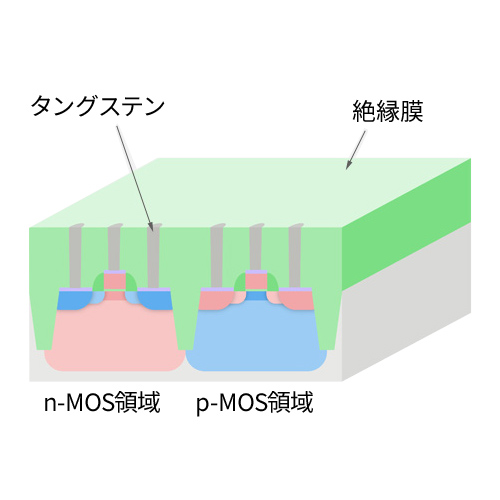

4. プラグタングステン研磨

表面を研磨し、余分なタングステン膜を除去し、コンタクトホールの中だけにタングステンを残します。

-

BEOL(Back End of Line:配線工程、半導体製造前工程の後半)

FEOLで形成した各素子を金属材材料で接続配線し、回路を形成します。

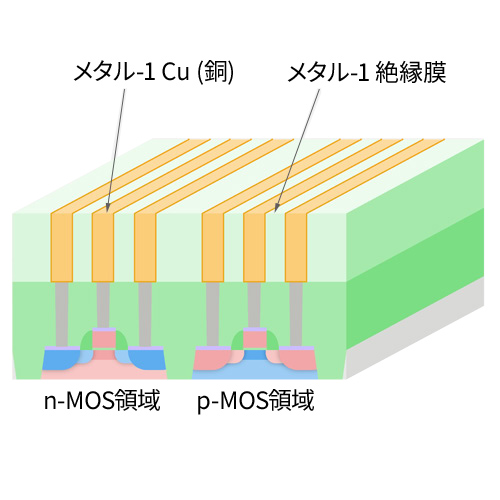

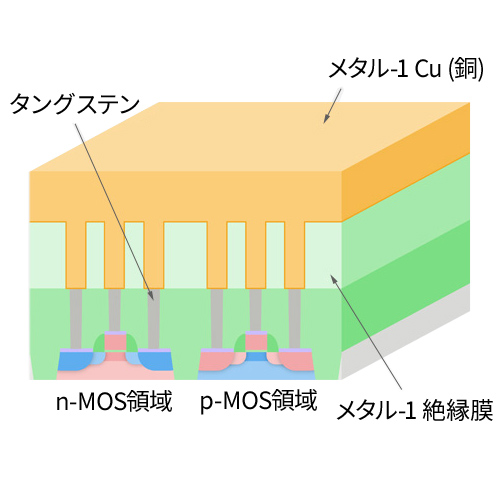

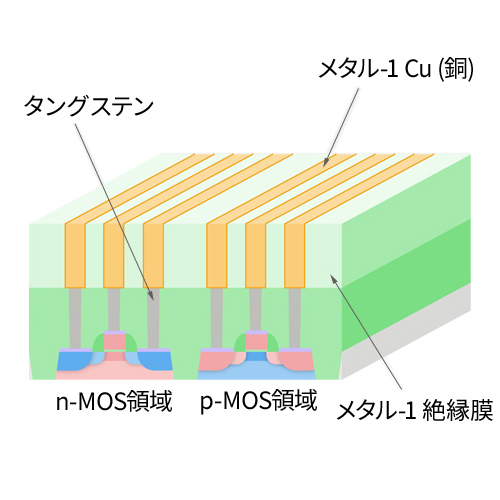

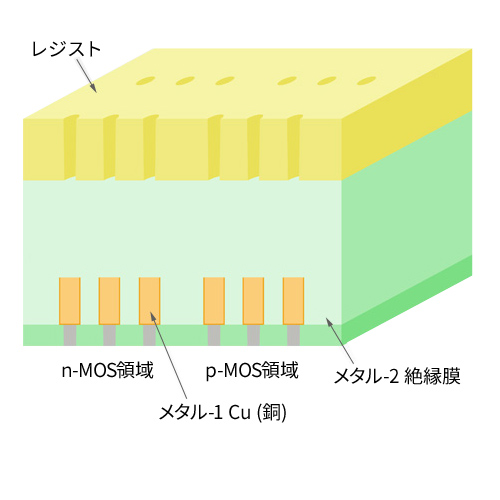

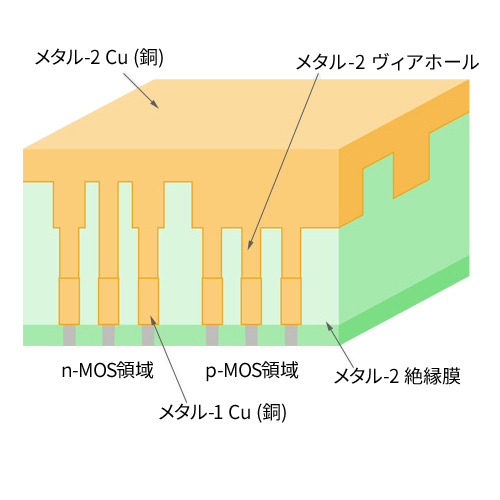

- 10メタル-1

-

メタル-1

-

絶縁膜を形成し、溝(トレンチ)を掘り、溝にCu(銅)を埋め込みます。

溝だけにCuを埋め込む方式をシングルダマシン(single damascene)と言います。

メタル-1Cu埋め込み:電気めっきでトレンチにCu膜を埋め込みます。

メタル-1Cu研磨:表面研磨でCu膜を除去し、溝の中だけにCuを残します。 -

1. メタル-1絶縁膜成長

シリコンウェハー表面にCVD法で厚いシリコン酸化膜などを形成します。

-

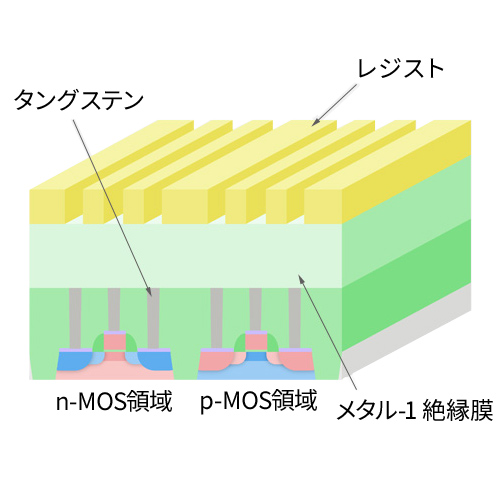

2. メタル-1トレンチレジストパターン形成

メタル-1トレンチ(溝)のレジストパターンを形成します。

-

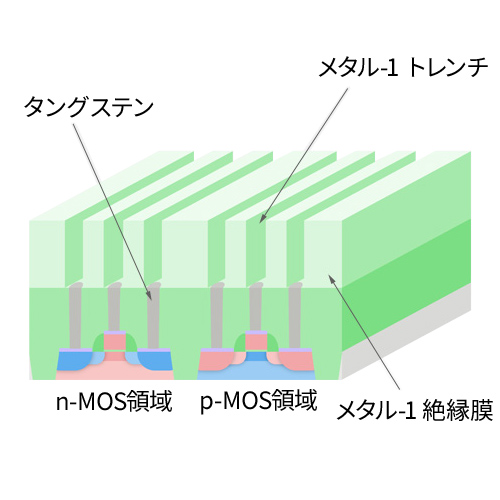

3. メタル-1トレンチエッチング

メタル-1トレンチレジストパターンをマスクにエッチング処理をおこない、絶縁膜にトレンチを形成します。

エッチング後、レジストパターンは除去します。 -

4. メタル-1Cu埋め込み

電気メッキでCu膜を形成し、トレンチに埋め込みます。

-

5. メタル-1Cu研磨

表面を研磨することで、余分なCu膜を除去し、トレンチの中だけにCuを残します。

-

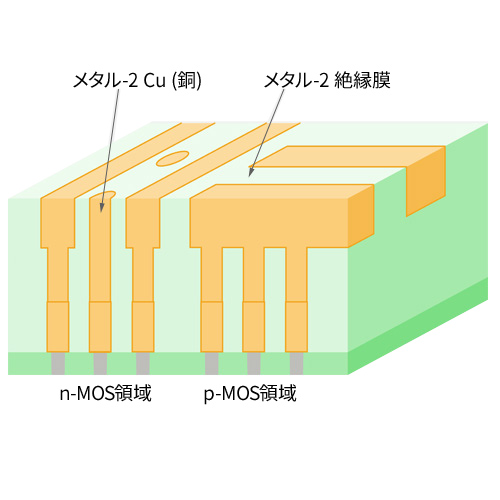

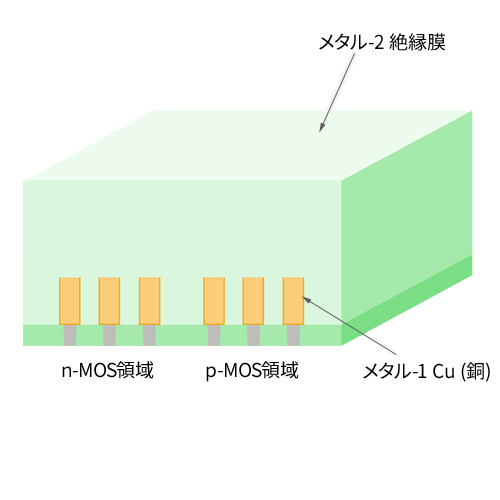

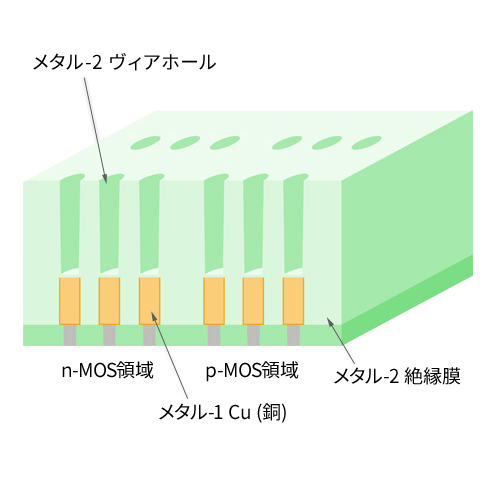

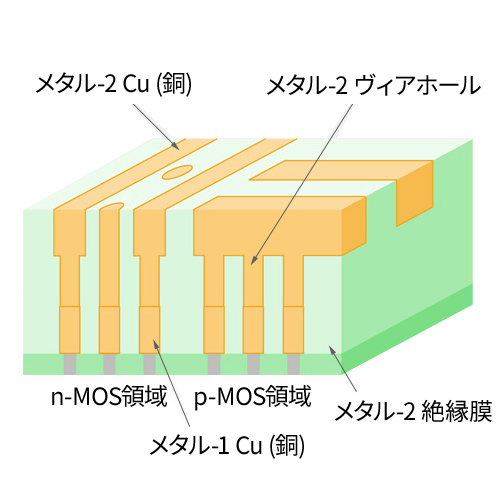

- 11メタル-2

-

メタル-2

-

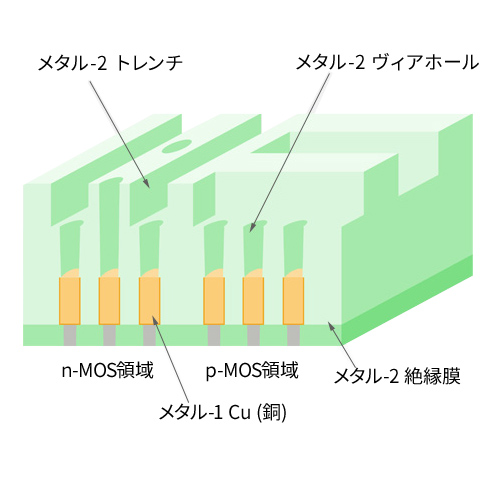

絶縁膜を形成し、穴、溝を掘り、穴と溝にCu(銅)を埋め込みます。穴と溝に同時にCuを埋め込む方式をデュアルダマシン(dual damascene)と言います。

メタル-2Cu埋め込み:電気めっきで穴と溝にCu膜を埋め込みます。

メタル-2Cu研磨:表面研磨でCu膜を除去し、穴と溝の中だけにCuを残します。 -

1. メタル-2絶縁膜成長

シリコンウェハー表面に、CVD法で厚いシリコン酸化膜などを形成します。

-

2. メタル-2ヴィアホールレジストパターン形成

ヴィアホールのレジストパターンを形成します。

-

3. メタル-2ヴィアホールエッチング

ヴィアホールパターンをマスクにエッチング処理をおこない、絶縁膜にヴィアホールを形成します。 エッチング後、レジストパターンは除去します。

-

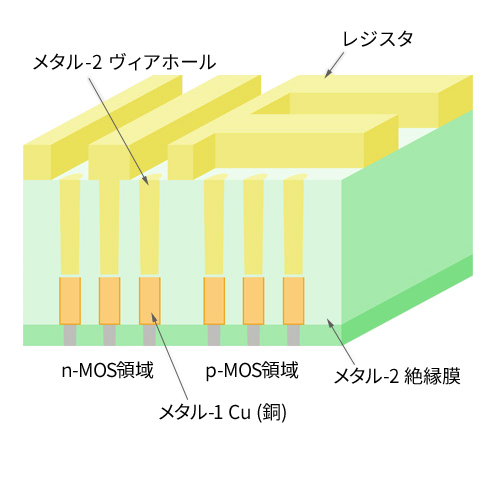

4. メタル-2トレンチレジストパターン形成

メタル-2トレンチ(溝)のレジストパターンを形成します。

-

5. メタル-2トレンチエッチング

メタル-2トレンチパターンをマスクにエッチング処理をおこない、絶縁膜にトレンチを形成します。 エッチング後、レジストパターンは除去します。

-

6. メタル-2Cu埋め込み

電気メッキでCu膜を形成し、ヴィアホール、トレンチに埋め込みます。

-

7. メタル-2Cu研磨

表面を研磨することで余分なCu膜を除去し、ヴィアホール、トレンチの中だけにCuを残します。

-